# B4661A Memory Analysis Software for Logic Analyzers

## Table of Contents

| Overview                                                            | 03 |

|---------------------------------------------------------------------|----|

| Licensed Views and Tools                                            | 05 |

| Traffic Overview                                                    | 06 |

| Transaction Decode                                                  | 07 |

| Performance Overview                                                | 07 |

| Address Access Mapping                                              | 08 |

| Refresh Rate Overview                                               | 09 |

| Details Tab                                                         | 10 |

| Speed Change Overview                                               | 10 |

| Mode Registers Overview                                             | 11 |

| GDDR6 Analysis                                                      | 11 |

| LPDDR5 Analysis and Compliance Validation (B4661A-6FP/6TP/6NP)      | 12 |

| DDR5 Analysis and Compliance Validation (B4661A-5FP/5TP/5NP)        | 14 |

| DDR3/4, LPDDR2/3/4, Analysis and ONFi Analysis (B4661A-4FP/4TP/4NP) | 16 |

| ONFi Analysis Viewer                                                | 17 |

| DDR and LPDDR Compliance Violation Analysis (B4661A-3FP/3TP/3NP)    | 19 |

| Real-Time Violations                                                | 20 |

| Post Process Compliance Tests                                       | 25 |

| LPDDR Decoder (B4661A-2FP/2TP/2NP)                                  | 29 |

| DDR Decoder with Physical Address Trigger (B4661A-1FP/1TP/1NP)      | 30 |

| B4661A Standard Software Features                                   | 31 |

| Standard Software Tools                                             | 31 |

| Default DDR Probing Configurations                                  | 31 |

| DDR Setup Assistant                                                 | 31 |

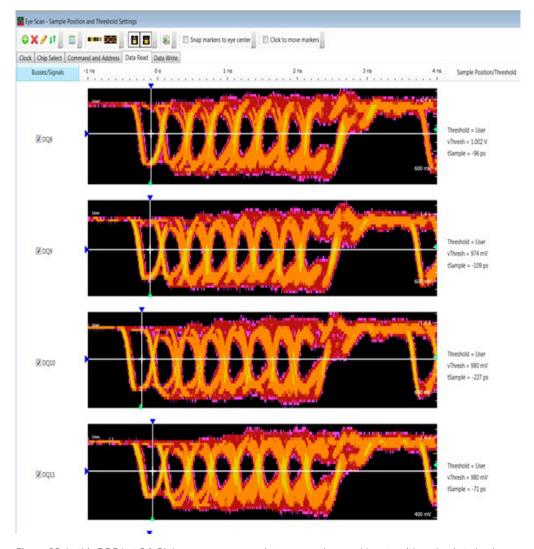

| DDR Eye Finder/Eye Scan                                             | 32 |

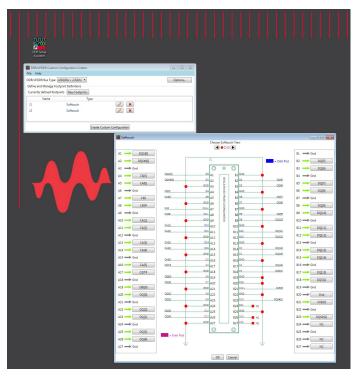

| DDR Configuration Creator                                           | 34 |

| B4661A Memory Analysis Software Characteristics                     | 35 |

| Logic Analyzer Compatibility                                        | 35 |

| Required Software                                                   | 35 |

| B4661A Memory Analysis Software Includes                            | 36 |

| Ordering Information                                                | 37 |

| B4661A Memory Analysis Software                                     | 37 |

| Related Literature                                                  | 38 |

#### Overview

The Keysight B4661A memory analysis software offers a suite of viewers and tools that include the industry's first protocol compliance violation testing capability across speed changes, a condensed traffic overview for rapid navigation to areas of interest in the logic analyzer trace, powerful performance analysis graphics, and DDR and LPDDR decoders. With the B4661A memory analysis software and a Keysight logic analyzer, users can monitor DDR3/4/5 or LPDDR2/3/4/5 systems to debug, improve performance, and validate protocol compliance. Powerful traffic overviews, multiple viewing choices, and real-time compliance violation triggering help identify elusive DDR/LPDDR system violations.

The Keysight B4661A memory analysis software provides four standard software features and seven licensed memory analysis options. GDDR6 analysis (B4661A-7FP/7TP/7NP) will be added in the 6.60 release in January 2020.

#### Licensed software options

- DDR decoder with physical address trigger tool (B4661A-1NP/1TP/1NP)

- LPDDR decoder with physical address trigger tool for LPDDR/2/3 (B4661A-2NP/2TP/2FP)

- DDR and LPDDR compliance violation analysis toolset (B4661A-3NP/3TP/3FP)

- Post-process compliance violation analysis

- Real-time compliance violation analysis

- DDR3/4, LPDDR2/3/4, and ONFi (Open NAND Flash interface) analysis (B4661A-4NP/4TP/4FP)

- DDR5 Analysis and Compliance SW (B4661A-5NP/5TP/5FP)

- LPDDR5 Analysis and Compliance SW (B4661A-6NP/6TP/6FP)

- GDDR6 analysis (B4661A-7FP/7TP/7NP)

#### Standard software features

- Default configurations for DDR and LPDDR probing solutions for Keysight logic analyzers

- DDR setup assistant

- DDR eye finder/eye scan

- DDR configuration creator

Use the optional compliance violation analysis and performance tools to further debug, validate, and optimize your memory system.

(See pages 5 to 28)

Start with Keysight's standard DDR/LPDDR tools to help setup your measurement (see pages 32 to 38).

- Standard configuration files for Keysight and FuturePlus interposers are provided.

- If a standard configuration is not available for your probing solution, the DDR/LPDDR configuration creator enables you to quickly create a configuration file relative to your system's layout.

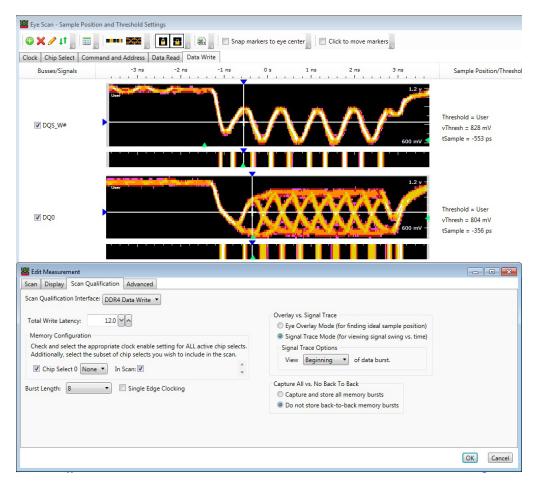

- Setup assistant and eye scan help you get sampling positions, thresholds, and triggering adjusted for a good measurement.

- Eye scan also helps you identify multiple signal integrity and execution issues before you even take your first trace capture with your logic analyzer module.

## Licensed Views and Tools

Use the licensed optional viewers and tools for analysis, transaction decode, performance, and compliance violation insight to further debug, validate, and optimize your memory system. Monitor memory activity and follow the memory signal flow like a device on the memory bus.

Chart of licensed viewers, tabs, and tools by recommended options for memory technologies.

| Licensed viewers,                      |              |                               | Features inclu     | ıded in Licensed (              | Options by Mem | ory Technology           | 1                        |             |

|----------------------------------------|--------------|-------------------------------|--------------------|---------------------------------|----------------|--------------------------|--------------------------|-------------|

| Tabs, and Tools                        | DDR2         | DDR3/4                        | LPDDR              | LPDDR2/3/4                      | ONFi           | DDR5                     | LPDDR5                   | GDDR6       |

| Listing decoder                        |              | IFP/1TP/1NP<br>listing decode |                    | 2FP/2TP/2NP<br>4 listing decode |                |                          |                          |             |

| Timeline view (ONFi)                   |              |                               |                    |                                 | B4661A-        |                          |                          |             |

| Payload tab (ONFi)                     |              |                               |                    |                                 | 4FP/4TP/4NP    |                          | _                        |             |

| Traffic overview                       |              | B4661A-                       |                    | B4661A-                         | ONFi analysis  | B4661A-                  | B4661A-                  | B4661-      |

| Transaction decode                     |              | 4FP/4TP/4NP                   |                    | 4FP/4TP/4NP                     | coverage       | 5FP/5TP/5NP              | 6FP/6TP/6NP              | 7FP/7TP/7NP |

| Details tab                            |              | DDR3/4,                       |                    | DDR3/4,                         |                | DDR5                     | LPDDR5                   | GDDR6       |

| Performance overview                   |              | LPDDR2/3/                     |                    | LPDDR2/3/                       |                | analysis and             | analysis and             | analysis    |

| Memory access overview                 |              | analysis<br>coverage          |                    | analysis<br>coverage            |                | compliance<br>validation | compliance<br>validation |             |

| Mode register overview                 |              |                               |                    |                                 |                |                          |                          |             |

| Speed change overview                  |              |                               |                    |                                 |                |                          |                          |             |

| Refresh rate overview                  |              |                               |                    |                                 |                |                          |                          |             |

| Post process compliance violation tool | B4661A-3FP/3 |                               |                    |                                 |                |                          |                          |             |

| Real time compliance violation tool    | DDR273/4 and | LPDDR2/3/4 comp               | oliance validatioi | n                               |                |                          |                          |             |

#### Traffic Overview

#### Command graphing

Using traffic overview, each command on the bus is a row in the table. Columns vary depending on the viewing option chosen. Users choose from the following viewing options:

- View all ranks in this mode, the table columns are "All ranks," "Rank 0," Rank 1," etc. The chart shows a different color dot on a different line for each rank.

- View a single rank The table columns are "All banks," "Bank 0," etc. (For DDR4, the columns are "All BG/BA", then all combinations of BG and BA.) The chart shows one line of dots. A choice for which bank to view in the chart is enabled.

- All banks The chart shows a dot for every command on the rank, regardless of bank. All dots are the same color.

- A single bank The chart shows a dot for commands that apply only to the selected bank.

- If the user has a multi-rank system and wants to see charts of each rank simultaneously, then they can use multiple applications of the tool.

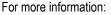

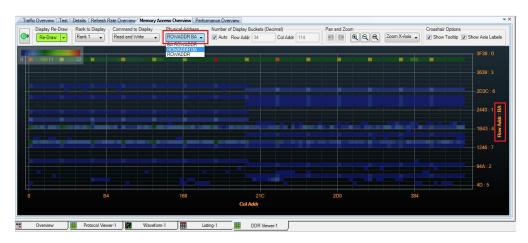

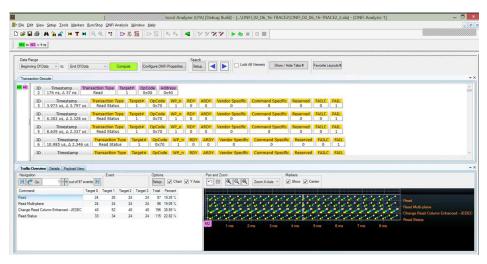

Figure 1. Traffic overview example: Graphing command activity by commands and banks across the captured trace from the Keysight logic analyzer.

The traffic overview containing transaction decode, summary calculations, meta-data, and graphing provides a condensed and insightful overview of system activity and enables powerful navigation to areas of interest.

#### Transaction Decode

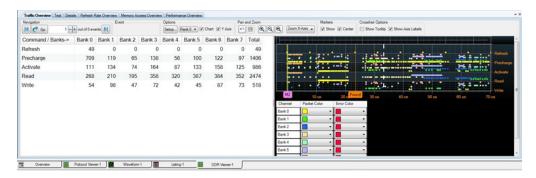

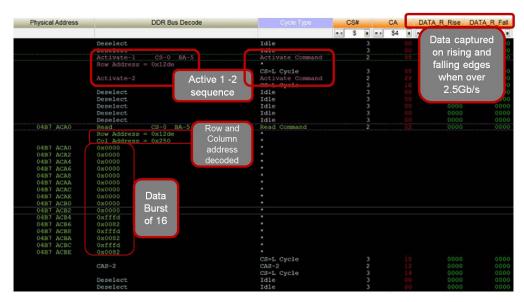

Figure 2. Transaction decode provides a high-level view of the memory protocol transactions.

### Performance Overview

#### Calculate and graph MByte data rates and % utilization

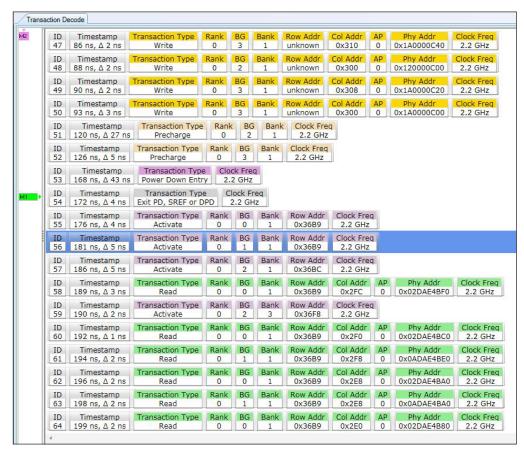

Figure 3. Customize performance views by changing sample rate and performance measurement selections.

The Performance Overview provides graphical and summary calculations of Read, Write, and Total MByte data rates along with a calculation and graph of the percentage of bus utilization. Users can choose to view the Read or Write Data rates as instantaneous, where each Read or Write command is represented with a dot.

## Address Access Mapping

Figure 4. Address access heat map enables an overview of the number of accesses at specific row and col addresses.

Figure 5. Users may also select row address and time as the axis on the address access heat map.

#### Refresh Rate Overview

DDR/LPDDR memory is volatile. The charge on the memory cells (capacitors) needs to be "refreshed" to ensure memory values are retained. For DDR and LPDDR memory, there are two ways to refresh

- Issue the refresh command.

- Issue a self-refresh command and put the memory into self-refresh mode for some length of time.

Figure 6. Refresh rate charts of LPDDR4 trace activity and quick pass/fail indication.

The refresh rate overview provides insight into refresh performance. It graphs refresh rate information for each sampled RW (refresh window) time window. By default, new refresh window samples are taken whenever there is a refresh event: refresh commands or entering/exiting self-refresh mode.

The X axis of this chart is time. The Y coordinate is the percent scale of expected refresh commands and self-refresh time found in the time window. The horizontal green line represents 100% for quick pass/fail indication. Red dots indicate areas that are under 100%.

Users can set the refresh window time (default 32 ms), the number (R) of refresh commands expected in the refresh window time, and the rank to display.

The highlighted box in the lower chart shows the refresh window time span for the sample at the "RW" marker point. The highlight box is red when under 100% and white when >= 100%.

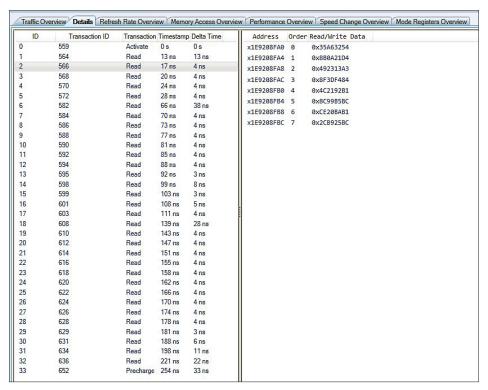

#### **Details Tab**

For LPDDR2/3/4/5, DDR3/4/5, and GDDR6, this tab displays the details of a selected memory transaction and all other transactions in the same sequence or 'open/closed page'. 'Pages' open with Activate commands, all Reads or Writes associated with the same Rank, Bank Group, Bank, and Row Address are part of the 'open page'. Pages close with an associated Precharge. When either a Read or Write transaction is selected, the Data associated with the selected Read or Write is also displayed with the associated address.

For ONFi, this tab displays the details of an ONFi transaction selected in the upper pane. You can also visualize an ONFi operation as a set of logically grouped commands in a sequence in the details tab.

Figure 7. The Details tab provides Page associations and associated Data for any highlighted Read or Write transaction.

## Speed Change Overview

Speed Change Overview provides a statistical as well as a graphical representation for an SDRAM's clock frequencies and frequency changes over a period of time.

- Higher pulses = higher frequency

- Duration of pulse = time at specific frequency

Figure 8. Speed changes on an LPDDR4 system.

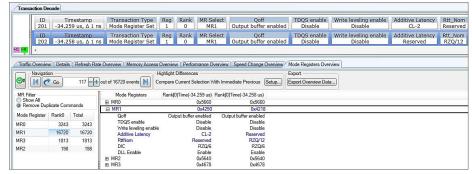

## Mode Registers Overview

#### Analyzing mode registersvalues

The Mode Registers Overview tab of the DDR/LPDDR Memory Analysis window provides you the following data from the computed memory transactions:

- A count of the Mode Register commands found for each of the mode registers of your SDRAM. For a multi-rank SDRAM, these counts are displayed for the mode registers of each of the ranks.

- A snapshot of the SDRAM's mode registers' values at a specific time.

- A comparison of the state of mode registers at different points in time.

or across ranks at a specific point in time. You can use the data displayed in this tab to get an insight into the state of the various operating parameters of the SDRAM that have been configured using various mode registers of the SDRAM. The comparison of the mode register values can help you understand and debug the SDRAM's behavior due to mode register value changes.

The following memory commands that are issued to set or modify mode registers of an SDRAM are included in the Mode Register Overview tab's data:

- Mode Register Set command

- Mode Register Write command

Figure 9. Mode Register Overview.

## GDDR6 Analysis (B4661A-7FP/7TP/7NP)

Using the B4661 memory analysis licensed software for GDDR6 analysis, navigation to problem areas is simplified with a powerful traffic overview that presents the GDDR6 traffic from the logic analyzer trace capture at the protocol level with user-selected filtering.

Licensed option B4661A-7FP/7TP/7NP consists of a GDDR6 analysis viewer with multiple tabs/views.

Key features (views and tools are described in more detail with screen shot examples under sections specific to each view or toolŁ)

- Traffic overview

- Graphs commands across the trace timeline

- Transaction decode

- Supports decoding of bank organization modes

- Decodes multipurpose (MPC) commands

- Details tab to see the data associated with each read or write transaction

- Performance overview

- Calculates and graphs data rates and % bus utilization

- Memory access overview

- Maps address accesses

- By row and Col ADDR

- By row ADDR and time

- Mode register overview

- Speed change overview

### LPDDR5 Analysis and Compliance Validation (B4661A-6FP/6TP/6NP)

Achieve greater insight faster using the B4661 memory analysis and compliance validation licensed software for LPDDR5 memory. LPDDR testing, protocol compliance and debug work has become more complex and time consuming over the years as data rates increase and the memory architectures become more complex. Using the LPDDR5 analysis and protocol compliance validation, navigation to problem areas is simplified with a powerful traffic overview that presents the LPDDR5 traffic from the logic analyzer trace capture at the protocol level with user-selected filtering.

Licensed option B4661A-6FP/6TP/6NP consists of a LPDDR5 analysis viewer with multiple tabs/views and two LPDDR5 protocol compliance tools, a Real-time DDR5 protocol compliance tool and a Post-process LPDDR5 protocol compliance tool.

#### LPDDR5 analysis

Key features (these views and tools are described in more detail with screen shot examples under sections specific to each view or tool.

- Traffic overview

- Graphs commands across the trace timeline

- Transaction decode

- Supports decoding of bank organization modes

- Decodes multipurpose (MPC) commands

- Self-Refresh entry/exit

- Details tab to see the data associated with each read or write transaction

- Performance overview

- Calculates and graphs MByte data rates and % bus utilization

- Memory access overview

- Maps Address accesses

- By row and Col ADDR

- By row ADDR and time

- Refresh rate overview

- Speed Change overview

- Mode Register overview

#### LPDDR5 protocol compliance tools

- LPDDR5 Real-time compliance violation analysis

- LPDDR5 Post-process violation analysis

Key features of both the post-process and real-time compliance violation tools:

- Test compliance violations across speed changes using the post-process compliance violation tool.

- Identify LPDDR5 state machine, protocol compliance, and protocol level bus cycle timing violations using either post-process or real-time tools.

- Save time with automated real-time LPDDR5 protocol compliance measurements and trace captures using the real-time compliance violation analysis tool.

- Edit parameters of the LPDDR5 standard preset tests easily using the enhanced parameter editing interface for both post-process and real-time tools.

#### Real-time LPDDR5 protocol compliance analysis

The automated real-time compliance analysis tool detects and captures state machine, protocol compliance, and protocol level bus cycle timing violations for LPDDR5. Real-time violation detection is an important advancement in DDR memory debug and valida—tion. Monitoring your LPDDR5 bus real-time means the Keysight logic analyzer will continuously monitor the bus for the selected test and trigger if it occurs within the specified time.

#### LPDDR5 Real-time testing enables

Monitoring for compliance violations while running specific routines on the system under test. Unique feature of real-time compliance tool allows custom regression test suites to be created from a valid logic analyzer trigger for any valid Keysight logic analyzer configuration compatible with the B4661A.

The real-time compliance violation analysis tool cycles through preset or user-edited parameters for a selectable time limit on each parameter to capture logic analyzer traces of the DDR5 bus, triggering on the violation. The tool allows the user to save multiple traces of violations and produces a summary report when complete.

#### Post-process LPDDR5 protocol compliance violation analysis tool

The post-process compliance violation analysis tool automates state machine, protocol compliance, and protocol level bus cycle timing violation detection across Keysight logic analyzer traces.HTML reports of test results show margin details for both passing and failing tests. Use the post-process compliance application tool to:

- Spot check logic analyzer traces for violations.

- Check logic analyzer trace captures leading up to system crashes for possible violations before the crash.

#### Post-process testing enables

- Compliance violation testing across speed changes.

- "Click to" and "mark violation" features to quickly navigate from the compliance tool to violations in the traffic overview graph, waveform, or listing window.

- Margin information on each parameter to understand the range relative to the specification.

### DDR5 Analysis and Compliance Validation (B4661A-5FP/5TP/5NP)

Achieve greater insight faster using the B4661 memory analysis and compliance validation licensed software for DDR5 memory. DDR testing, protocol compliance and debug work has become more complex and time consuming over the years as data rates increase and the memory architectures become more complex. Using the DDR5 analysis and protocol compliance SW, navigation to problem areas is simplified with a powerful traffic overview that presents the DDR5 traffic from the logic analyzer trace capture at the protocol level with user-selected filtering.

Licensed option B4661A-5FP/5TP/5NP consists of a DDR5 analysis viewer with multiple tabs/views and two DDR5 protocol compliance tools, a Real-time DDR5 protocol compliance tool and a Post-process DDR5 protocol compliance tool.

#### DDR5 analysis

Key features (these views and tools are described in more detail with screen shot images under sections specific to each view or tool.

- Traffic overview

- Graphs commands across the trace timeline

- Transaction decode

- Supports decoding of low power data transfers

- Decodes multipurpose (MPC) commands

- Self-Refresh entry/exit

- Details tab to see the data associated with each read or write transaction

- Performance overview

- Calculates and graphs MByte data rates and % bus utilization

- Memory access overview

- Maps Address accesses

- By row and Col ADDR

- By row ADDR and time

- Refresh rate overview

- Speed Change overview

- Mode Register Overview

#### DDR5 protocol compliance tools

- DDR5 Real-time protocol compliance violation analysis

- DDR5 Post-process protocol compliance violation analysis

Key features of both the post-process and real-time compliance violation tools:

- Test compliance violations across speed changes using the post-process compliance violation tool.

- Identify DDR5 state machine, protocol compliance, and protocol level bus cycle timing violations using either post-process or real-time tools.

- Save time with automated real-time DDR5 protocol compliance measurements and trace captures using the real-time compliance violation analysis tool.

- Edit parameters of the DDR5 standard preset tests easily using the enhanced parameter editing interface for both post-process and real-time tools.

#### Real-time DDR5 compliance analysis

The automated real-time compliance analysis tool detects and captures state machine, protocol compliance, and protocol level bus cycle timing violations for DDR5. Real-time violation detection is an important advancement in DDR memory debug and validation. Monitoring your DDR5 bus real-time means the Keysight logic analyzer will continuously monitor the bus for the selected test and trigger if it occurs within the specified time.

#### Real-time testing enables

Monitoring for compliance violations while running specific routines on the system under test. Unique feature of real-time compliance tool allows custom regression test suites to be created from a valid logic analyzer trigger for any valid Keysight logic analyzer configura—tion compatible with the B4661A.

The real-time compliance violation analysis tool cycles through preset or user-edited parameters for a selectable time limit on each parameter to capture logic analyzer traces of the DDR5 bus, triggering on the violation. The tool allows the user to save multiple traces of violations and produces a summary report when complete.

#### Post-process DDR5 compliance violation analysis tool

The post-process compliance violation analysis tool automates state machine, protocol com-pliance, and protocol level bus cycle timing violation detection across Keysight logic analyzer traces.HTML reports of test results show margin details for both passing and failing tests. Use the post-process compliance application tool to:

- Spot check logic analyzer traces for violations.

- Check logic analyzer trace captures leading up to system crashes for possible violations before the crash.

#### Post-process testing enables

- Compliance violation testing across speed changes.

- "Click to" and "mark violation" features to quickly navigate from the compliance tool to violations in the traffic overview graph, waveform, or listing window.

- Margin information on each parameter to understand the range relative to the specification.

## DDR3/4, LPDDR2/3/4, Analysis and ONFi Analysis (B4661A-4FP/4TP/4NP)

Licensed option B4661A-4FP/4TP/4NP consists of two different analysis viewers. One viewer covers DDR3/4 and LPDDR2/3/4 analysis and the second viewer provides ONFi analysis.

#### DDR3/4 and LPDDR2/3/4 Analysis Viewer

#### Key features

- Traffic overview

- Command graphing

- Transaction decode

- Performance overview

- Calculate and graph MByte data rates and % bus utilization

- Memory access overview, address access mapping

- By row and Col ADDR

- By row ADDR and time

- Refresh rate overview

- Speed Change Overview

- Mode register overview

#### ONfi (Open NAND Flash interface) Analysis Viewer

#### Key features

- Timeline View

- Payload tab

- Details tab

- Customizable features to support Toggle mode and proprietary NAND protocols

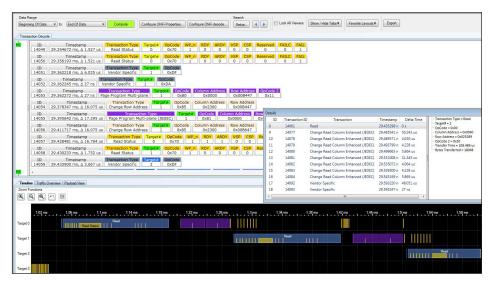

## ONFi Analysis Viewer

Enhanced ONFi (open NAND flash interface) analysis is included in the B4661A Memory analysis SW, licensed option -4NP/TP/FP.

- Follow ONFi traffic flow using "Transaction Decode" and "Traffic Overview" views.

- Navigate quickly across multiple ONFi targets using the condensed ONFi analysis "Timeline" view.

- Save time by visualizing an ONFi operation as a set of logically associated commands in a sequence, using the "Details" view of the ONFi transactions.

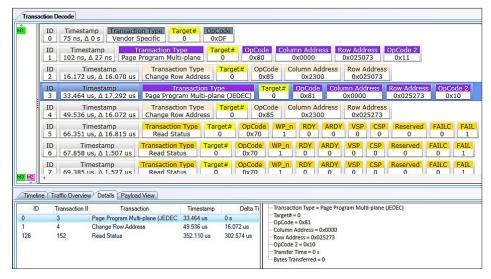

Figure 10. ONFi Transaction Decoder, Details, and Timeline views increase insight into ONFi traffic.

Figure 11. ONFi Traffic Overview with Transaction Decoder provide statistical information and a graphical overview of ONFi transactions over time to allow rapid navigation through the transactions.

Figure 12. Save time by visualizing an ONFi operation as a set of logically associated commands inclueing the transation times and delta times.

NAND Memory Controllers often use commands and protocols that are not part of the ONFi Standard.

Proprietary intellectual property can be involved with controlling NAND memory. The ONFi analysis viewer includes the ability for a user to define custom opcodes and sequence associations using xml files. Characteristics of the customization feature include:

- Single line xml for single opcode sequences.

- Longer sequences programmable using simple extensible syntax.

- Support for a wide variety of CMD/ADDR/DATA combinations.

- Customizable Decode text and color.

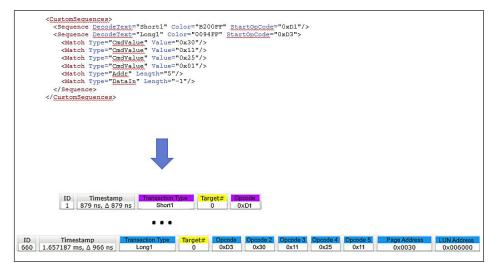

Figure 13. Define custom opcodes and sequence associations.

## DDR and LPDDR Compliance Violation Analysis (B4661A-3FP/3TP/3NP)

The DDR and LPDDR compliance violation analysis toolset provides two tools under one license. Both compliance tools cover DDR, DDR2, DDR3, DDR4, LPDDR, LPDDR2, LPDDR3, and LPDDR4. The two tools are:

- Real-time compliance violation analysis

- Post-process violation analysis

## Keysight often enhances compliance SW parameters. For the latest list of parameters for each technology, download the latest Logic analyzer and B4661A SW.

Key features of both the post-process and real-time compliance violation tools:

- Test compliance violations across speed changes using the post-process compliance violation tool.

- Identify DDR/2/3/4 or LPDDR/2/3/4 state machine, protocol compliance, and protocol level bus cycle timing violations using either post-process or real-time tools.

- Save time with automated real-time DDR2/3/4 or LPDDR2/3/4 protocol compliance measurements and trace captures using the real-time compliance violation analysis tool.

- Edit parameters of the DDR/LPDDR standard preset tests easily using the enhanced parameter editing interface for both post-process and real-time tools.

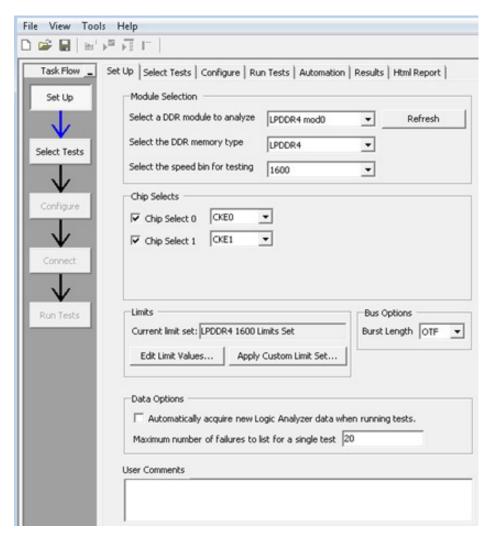

Figure 14. Both the real-time and post-process compliance tools provide user interfaces with pull-down selections to make setup easy.

Post-process and real-time compliance tools both contain dialogs with descriptions of the parameter values for ease of editing.

#### Real-time compliance analysis

The automated real-time compliance analysis tool detects and captures state machine, protocol compliance, and protocol level bus cycle timing violations for DDR3/4 or LPDDR2/3/4. Real-time violation detection is an important advancement in DDR memory debug and validation. Monitoring your DDR bus real-time means the Keysight logic analyzer will continuously monitor the bus for the selected test and trigger if it occurs within the specified time frame. Beyond monitoring your DDR3/4 or LPDDR2/3/4 system real-time for elusive violations, designers can also monitor other digital system continuously for elusive, intermittent violations in protocol compliance or bus level timing.

#### Real-time testing enables

- Monitoring for compliance violations while running specific routines on the system under test.

- Unique feature of real-time compliance tool allows custom regression test suites to be created from a valid logic analyzer trigger for any valid Keysight logic analyzer configuration compatible with the B4661A.

The real-time compliance violation analysis tool cycles through preset or user-edited parameters for a selectable time limit on each parameter to capture logic analyzer traces of the complete ADD/CMD/DATA capture of the DDR/LPDDR bus triggering on the violation. The tool allows the user to save multiple traces of violations and produces a summary report when complete.

#### Real-Time Violations

| READ or WRITE to an ina  | ctive row                                                                 |

|--------------------------|---------------------------------------------------------------------------|

| REFRESH to an active ba  | nk                                                                        |

| ACTIVATE to an active ba | ınk                                                                       |

| Real-time violations     |                                                                           |

| Compliance parameter     | Real-time compliance tests                                                |

| Parameters common to     | DDR, DDR2, DDR3, and LPDDR                                                |

| tRASmin                  | ACTIVATE to PRECHARGE must be >= tRASmin                                  |

| tRASmax                  | ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax                   |

| tRCD                     | ACTIVATE to READ/WRITE must be >= tRCD                                    |

| tRP                      | PRECHARGE to ACTIVATE/PRECHARGE must be >= tRP                            |

| tRTP                     | READ to PRECHARGE must be >= tRTP                                         |

| tDRW                     | READ to WRITE must be >= tDRW                                             |

| tDWP                     | WRITE to PRECHARGE must be >= tDWP                                        |

| tCCD                     | WRITE to WRITE, READ to READ must be >= tCCD                              |

| tRFC                     | REFRESH to valid command (non_NOP/DESELECT) must be >= tRFC               |

| tRRD                     | ACTIVATE to ACTIVATE (different banks) must be >= tRRD                    |

| tRC                      | ACTIVATE to ACTIVATE (same bank) must be >= tRC                           |

| tREFI                    | REFRESH to REFRESH <= tREFI*9                                             |

| tMRD                     | MRS (Mode Register Set) to MRS must be >= tMRD                            |

| Additional DDR3 compli   | ance parameters                                                           |

| tZQoper                  | Long cal (normal operation) to valid command must be >= tZQoper           |

| tZQCS                    | Short calibration (normal operation) to any valid command must be > tZQCS |

| tMOD                     | MRS (MODE Register Set) to valid command must be >= tMOD                  |

| tREFPDEN                 | REFRESH to power down entry >= tREFPDEN                                   |

| tRDPDEN                  | READ to power down entry >= tRDPDEN                                       |

| tWRPDEN                  | WRITE to power down entry >= tWRPDEN                                      |

| tXPR                     | Exit RESET from CKE high to valid command >= tXPR                         |

| tXSDLL                   | Self refresh exit to valid command with DLL must be >= tXSDLL             |

## Real-Time Violations (Continued)

|                         | Real-time compliance tests                                                     |  |  |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------------|--|--|--|--|--|--|

| Additional DDR4 complia | •                                                                              |  |  |  |  |  |  |

| tRASmin                 | ACTIVATE to PRECHARGE must be >= tRASmin                                       |  |  |  |  |  |  |

| tRASmax                 | ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax                        |  |  |  |  |  |  |

| tRCD                    | ACTIVATE to READ/WRITE must be >= tRCD                                         |  |  |  |  |  |  |

| tRP                     | PRECHARGE to ACTIVATE/PRECHARGE must be >= tRP                                 |  |  |  |  |  |  |

| tRTP                    | READ to PRECHARGE must be >= tRTP                                              |  |  |  |  |  |  |

| tDRW                    | READ to WRITE must be >= tDRW                                                  |  |  |  |  |  |  |

| tDWP                    | WRITE to PRECHARGE must be >= tDWP                                             |  |  |  |  |  |  |

| tDWR                    | WRITE to READ must be > tDWR                                                   |  |  |  |  |  |  |

| tCCD_L                  | WRITE to WRITE, same bank group must be >= tCCD_L                              |  |  |  |  |  |  |

| tRFC                    | REFRESH to valid command (non_NOP/DESELECT) must be >= tRFC                    |  |  |  |  |  |  |

| tRRD_L                  | ACTIVATE to ACTIVATE (same bank group) must be >= tRRD_L                       |  |  |  |  |  |  |

| tRC                     | ACTIVATE to ACTIVATE (same bank) must be >= tRC                                |  |  |  |  |  |  |

| tREFI                   | REFRESH to REFRESH <= tREFI*9                                                  |  |  |  |  |  |  |

| tZQoper                 | Long cal (normal operation) to valid command must be >= tZQoper                |  |  |  |  |  |  |

| tZQCS                   | Short calibration (normal operation) to any valid command must be > tZQCS      |  |  |  |  |  |  |

| tMRD                    | MRS (MODE Register Set) to MRS must be >= tMRD                                 |  |  |  |  |  |  |

| tMOD                    | MRS (MODE Register Set) to valid command must be >= tMOD                       |  |  |  |  |  |  |

| trefpden                | REFRESH to power down entry >= tREFPDEN                                        |  |  |  |  |  |  |

| tRDPDEN                 | READ to power down entry >= tRDPDEN                                            |  |  |  |  |  |  |

| tWRPDEN                 | WRITE to power down entry >= tWRPDEN                                           |  |  |  |  |  |  |

| tXPR                    | Exit RESET from CKE high to valid command >= tXPR                              |  |  |  |  |  |  |

| tXSDLL                  | Self refresh exit to valid command with DLL must be >= tXSDLL                  |  |  |  |  |  |  |

| tCKE                    | Duration of CKE high / low >= tCKE                                             |  |  |  |  |  |  |

| Additional LPDDR2/3 co  |                                                                                |  |  |  |  |  |  |

| tRASmin                 | ACTIVATE to PRECHARGE must be >= tRASmin                                       |  |  |  |  |  |  |

| tRASmax                 | ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax                        |  |  |  |  |  |  |

| tRCD                    | ACTIVATE to READ/WRITE must be >= tRCD                                         |  |  |  |  |  |  |

| tRTP                    | READ to PRECHARGE must be >= tRTP                                              |  |  |  |  |  |  |

| tDRW                    | READ to WRITE must be >= tDRW                                                  |  |  |  |  |  |  |

| tDWP                    | WRITE to PRECHARGE must be >= tDWP                                             |  |  |  |  |  |  |

| tDWR                    | WRITE to READ must be > tDWR                                                   |  |  |  |  |  |  |

| tCCD                    | WRITE to WRITE, must be >= tCCD                                                |  |  |  |  |  |  |

| tRRD                    | ACTIVATE to ACTIVATE (different banks) must be >= tRRD                         |  |  |  |  |  |  |

| tZQCL                   | Long calibration command to any valid command (or CKE low) must be > tZQCL     |  |  |  |  |  |  |

| tZQCS                   | Short calibration command to any valid command (or CKE low) must be > tZQCS    |  |  |  |  |  |  |

| tZQINIT                 | Init calibration command to any valid command (or CKE low) must be > tZQINIT   |  |  |  |  |  |  |

| tZQRESET                | Reset calibration command to any valid command (or CKE low) must be > tZQRESET |  |  |  |  |  |  |

| tMRW                    | MRW command to any valid command (or CKE low) must be > tMRW                   |  |  |  |  |  |  |

| tMRR                    | MRR command to any valid command (or CKE low) must be > tMRR                   |  |  |  |  |  |  |

| tRFCab                  | REFRESH (all banks) to Active or Refresh must be > tRFCab                      |  |  |  |  |  |  |

| tRFCpb                  | REFRESH (per bank) to Activate (same bank) or REFRESH must be > tRFCpb         |  |  |  |  |  |  |

| tRPab                   | PRECHARGE (all banks) to ACTIVE (any bank) must be >= tRPab                    |  |  |  |  |  |  |

| tRPpb                   | PRECHARGE (per bank) to ACTIVE (same bank) must be >= tRPpb                    |  |  |  |  |  |  |

| tCKE                    | Duration of CKE high / low >= tCKE                                             |  |  |  |  |  |  |

| tXP                     | Exit Power down to any valid command >= tXP                                    |  |  |  |  |  |  |

| tXSR                    | Exit self refresh to any valid command >=tXSR                                  |  |  |  |  |  |  |

|                         |                                                                                |  |  |  |  |  |  |

## Real-Time Violations (Continued)

| Compliance parameter   | Real-time compliance tests                                                                          |  |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Additional LPDDR4 comp | pliance parameters                                                                                  |  |  |  |  |  |

| tRASmin                | ACTIVATE to PRECHARGE must be >= tRASmin                                                            |  |  |  |  |  |

| tRASmax                | ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax                                             |  |  |  |  |  |

| tRCD                   | ACTIVATE to READ/WRITE must be >= tRCD                                                              |  |  |  |  |  |

| tRTP                   | READ to PRECHARGE must be >= tRTP                                                                   |  |  |  |  |  |

| tCCD                   | READ -1 or any write (any bank) to READ-1 or any write (any bank) must be >= tCCD                   |  |  |  |  |  |

| tCCDMW                 | Any write to MASKED WRITE (same bank) must be > =tCCDMW                                             |  |  |  |  |  |

| tRRD                   | ACTIVATE-2 to ACTIVATE-2 (different banks) must be >=tRRD                                           |  |  |  |  |  |

| tMRW                   | MRW-2 to any valid command must be >= tMRW                                                          |  |  |  |  |  |

| tMRR                   | MRR-1 to any valid command must be >= tMRR                                                          |  |  |  |  |  |

| tRPab                  | PRECHARGE (all banks) to ACTIVATE-2/REFRESH (any bank) >= tRPab                                     |  |  |  |  |  |

| tRPpb                  | PRECHARGE (per bank) to ACTIVATE-2 (same bank) or REFRESH (same bank or all banks) must be >= tRPpb |  |  |  |  |  |

| tXSR                   | Exit self refresh to any valid command >= tXSR                                                      |  |  |  |  |  |

| tPPD                   | Precharge (any bank to Precharge (any bank) must be >= tPPD                                         |  |  |  |  |  |

| tRFCab                 | REFRESH (all banks to ACTIVATE-2 or REFRESH >= tRFCab                                               |  |  |  |  |  |

| tRFCpd                 | REFRESH (per bank) to ACTIVATE-2 (same bank) or REFRESH > tRFCpb                                    |  |  |  |  |  |

| tREFI                  | REFRESH command to REFRESH command must be <=tREFI*9                                                |  |  |  |  |  |

| tCKE                   | Duration of CKE high / low >= tCKE                                                                  |  |  |  |  |  |

| tESCKE                 | Self Refresh Entry command to CKE low must be >= tESCKE                                             |  |  |  |  |  |

| tCMDCKE                | Any valid command to CKE low must be >= tCMDCKE                                                     |  |  |  |  |  |

| tCKEHCMD               | Exit powerdown to any valid command >= tCKEHCMD                                                     |  |  |  |  |  |

| tMMRRIa                | Exit powerdown to MRR >= tMRRIa (where tMRRIa = tXP (tCKEHCMD) + tMRRI)                             |  |  |  |  |  |

| BL16                   | Write/Read/Precharge - BL16 - Select these tests if your system uses fixed BL16                     |  |  |  |  |  |

| BL32                   | Write/Read/Precharge - BL16 - Select these tests if your system uses fixed BL32                     |  |  |  |  |  |

| BL OTF                 | Write/Read/Precharge - BL16 - Select these tests if your system uses Burst length OTF (on the fly)  |  |  |  |  |  |

| MWtoP                  | MASKED WRITE-1 to PRECHARGE (same bank) >= MWtoP                                                    |  |  |  |  |  |

| MWtoR                  | MASKED WRITE-1 to READ (same bank) >= MWtoR                                                         |  |  |  |  |  |

| RFtoLAT                | RD_FIFO to ZQCALLATCH >= RFtoLAT                                                                    |  |  |  |  |  |

| RFtoLAT                | RD_CALIBRATION to ZQCALLATCH >= RFtoLAT                                                             |  |  |  |  |  |

| RFtoLAT                | MRR to ZQCALLATCH >= RFtoLAT                                                                        |  |  |  |  |  |

| WFtoLAT                | WR_FIFO to ZQCALLATCH >= WFtoLAT                                                                    |  |  |  |  |  |

| WFtoLAT                | MASKED WRITE-1 to ZQCALLATCH >= WFtoLAT                                                             |  |  |  |  |  |

| tZQCAL                 | ZQCALSTART to ZQCALLTACH >= tZQCAL                                                                  |  |  |  |  |  |

| tZQLAT                 | ZQCALLATCH to any valid command >= tZQLAT                                                           |  |  |  |  |  |

| tZQRESET               | ZQCALRESET to any valid COMMAnd >= tZQRESET                                                         |  |  |  |  |  |

#### Post-process compliance violation analysis tool

The post-process compliance violation analysis tool automates state machine, protocol compliance, and protocol level bus cycle timing violation detection across Keysight logic analyzer traces. HTML reports of test results show margin details for both passing and failing tests.

Use the post-process compliance application tool to:

- Spot check logic analyzer traces for violations.

- Check logic analyzer trace captures leading up to system crashes for possible violations before the crash.

#### Post-process testing enables:

- Compliance violation testing across speed changes.

- "Click to" and "mark violation" features to quickly navigate from the compliance tool to violations in the traffic overview graph, waveform, or listing window.

- Margin information on each parameter to understand the range relative to the specification.

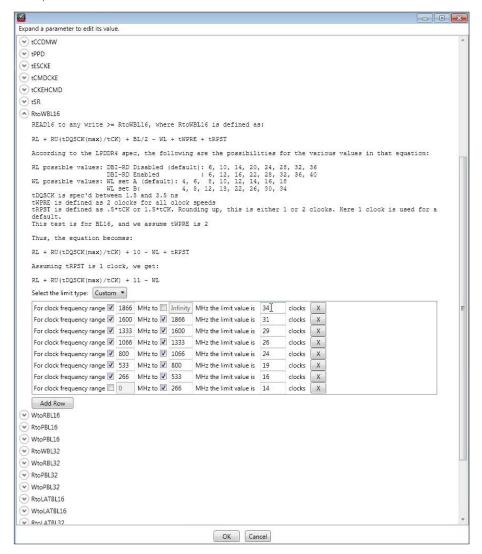

Figure 15. Speed ranges can be added in the post-process compliance tool for any parameter that has different criteria based on speed.

| et Up   Select Tests   Configure   Run   Aut | omate Results HTML Report               |                   |      |              |                       |        |

|----------------------------------------------|-----------------------------------------|-------------------|------|--------------|-----------------------|--------|

| Test Name                                    |                                         |                   |      | lue Margin % | Pass Limits           | # Tria |

| ✓ ACTIVATE to PRECHARGE/Auto-PRECHA          | RGE must be <= tRASmax                  |                   | Pass | 129E+01      | VALUE <= 70.200 μs    | 1      |

| XACTIVATE to PRECHARGE must be >= t          | RASmin                                  |                   | Fail | -36.4        | VALUE >= 35.0 ns      | 1      |

| X ACTIVATE to READ/WRITE must be >=          | tRCD                                    |                   | Fail | -25.7        | VALUE >= 14.96 ns     | 1      |

| PRECHARGE to ACTIVATE must be >= t           | RP                                      |                   | Fail | -25.7        | VALUE >= 14.96 ns     | 1      |

| READ to PRECHARGE must be >= tRTP            |                                         |                   | Fail | -17.2        | max(7.5ns, 4CK)       | 1      |

| ✓ READ to WRITE must be >= tDRW              |                                         |                   | Pass | 360.0        | RL + BL/2 + 2tCK - WL | 1      |

| WRITE to PRECHARGE must be >= tDW            | /P                                      |                   | Fail | -20.8        | WL + BL/2 + tWR       | 1      |

| WRITE to READ (different bank group)         | must be >= tDWR_S                       |                   | Fail | -17.9        | WL + BL/2 + tWTR_S    | 1      |

| X WRITE to READ (same bank group) mus        | st be >= tDWR_L                         |                   | Fail | -16.7        | WL + BL/2 + tWTR_L    | 1      |

| ✓ WRITE to WRITE (different bank group)      | , READ to READ (different bank group)   | must be >= tCCD_S | Pass | 0.0          | VALUE >= 4 CK         | 1      |

| WRITE to WRITE (same bank group), R          | EAD to READ (same bank group) must b    | oe >= tCCD_L      | Fail | -32.2        | max(6.25ns, 5CK)      | 1      |

| REFRESH to non-NOP/DES must be >=            | trfc                                    |                   | Fail | -42.7        | VALUE >= 350.0 ns     | 1      |

| X ACTIVATE to ACTIVATE (different bank       | group) must be >= tRRD_S                |                   | Fail | -49.3        | max(6ns, 4CK)         | 1      |

| X ACTIVATE to ACTIVATE (same bank gro        | up, different bank addr) must be >= tRI | RD_L              | Fail | -34.4        | max(7.5ns, 4CK)       | 1      |

| Four ACTIVATE window (different banks        | ) must be >= tFAW                       |                   | Fail | -41.7        | max(35ns, 28CK)       | 1      |

| X ACTIVATE to ACTIVATE (same bank)/Re        | fresh must be >= tRC                    |                   | Fail | -33.1        | VALUE >= 50.0 ns      | 1      |

| Certain RCW access to next control wor       | d access >= tMRD_L                      |                   | N/A  |              | VALUE >= 16 CK        | 1      |

| Certain RCW access to next control wor       | d access >= tMRD_L2                     |                   | N/A  |              | VALUE >= 32 CK        | 1      |

| Mode Register Set command to valid co        | mmand (other than MRS) >= tMOD          |                   | N/A  |              | max(15ns, 24CK)       | 1      |

| Parameter                                    | Value                                   |                   |      |              |                       |        |

| tRASmin                                      | Fail                                    |                   |      |              |                       |        |

| Additional Info                              |                                         |                   |      |              |                       |        |

| Acquisition Time                             | Triggered on 2/23/2016 at 4:53:31 PM    |                   |      |              |                       |        |

| Number of tests                              | 633417                                  |                   |      |              |                       |        |

| Number of failures                           | 73540                                   |                   |      |              |                       |        |

| Number of failures listed                    | 20                                      |                   |      |              |                       |        |

| Mark all failures listed                     |                                         |                   |      |              |                       |        |

| Mark and jump to worst case failure listed   |                                         |                   |      |              |                       |        |

| Edit limit value                             |                                         |                   |      |              |                       |        |

|                                              |                                         |                   |      |              |                       |        |

| State Pair                                   | Margin/Time/Clocks/Clock_Frequency      |                   |      |              |                       |        |

|                                              |                                         |                   |      |              |                       |        |

| 1. 175 231                                   | -0.2%, 34.88 ns, 56 CK, 1.603 GHz       |                   |      |              |                       |        |

| 2. 252 301                                   | -12.6%, 30.56 ns, 49 CK, 1.603 GHz      |                   |      |              |                       |        |

Figure 16. The post-process compliance tool includes hyperlinks to jump quickly to and/or mark violations and worst-case violations in the logic analyzer traces, transaction overview, and listing windows.

## Post Process Compliance Tests

| State machine vio<br>READ to WRITE to | lations common to DDR, DDR2, DDR3, DDR4 and LPDDR, LPDDR2, LPDDR3, LPDDR4 an inactive row |

|---------------------------------------|-------------------------------------------------------------------------------------------|

| REFRESH to an act                     |                                                                                           |

| ACTIVATE to an ac                     |                                                                                           |

| Post-process viola                    | ations                                                                                    |

| •                                     | neter Post-process compliance tests                                                       |

| Parameters comm                       | non to DDR, DDR2, DDR3, and LPDDR                                                         |

| tRASmin                               | ACTIVATE to PRECHARGE must be >= tRASmin                                                  |

| tRASmax                               | ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax                                   |

| tRCD                                  | ACTIVATE to READ/WRITE must be >= tRCD                                                    |

| tRP                                   | PRECHARGE to ACTIVATE/PRECHARGE must be >= tRP                                            |

| tRTP                                  | READ to PRECHARGE must be >= tRTP                                                         |

| tDRW                                  | READ to WRITE must be >= tDRW                                                             |

| tDWP                                  | WRITE to PRECHARGE must be >= tDWP                                                        |

| tDWR                                  | WRITE to READ must be > tDWR                                                              |

| tCCD                                  | WRITE to WRITE, READ to READ must be >= tCCD                                              |

| tRFC                                  | REFRESH to valid command (non_NOP/DESELECT) must be >= tRFC                               |

| tRRD                                  | ACTIVATE to ACTIVATE (different banks) must be >= tRRD                                    |

| tFAW                                  | Four ACTIVATE window (different banks) must be>= tFAW                                     |

| tRC                                   | ACTIVATE to ACTIVATE (same bank) must be >= tRC                                           |

| tREFI                                 | REFRESH to REFRESH <= tREFI*9                                                             |

| tMRD                                  | MRS (Mode Register Set) to MRS must be >= tMRD                                            |

| Additional DDR3 o                     | compliance parameters                                                                     |

| tZQoper                               | Long cal (normal operation) to valid command must be >= tZQoper                           |

| tZQCS                                 | Short calibration (normal operation) to any valid command must be > tZQCS                 |

| tMOD                                  | MRS (MODE Register Set) to valid command must be >= tMOD                                  |

| tREFPDEN                              | REFRESH to power down entry >= tREFPDEN                                                   |

| tRDPDEN                               | READ to power down entry >= tRDPDEN                                                       |

| tWRPDEN                               | WRITE to power down entry >= tWRPDEN                                                      |

| tXPR                                  | Exit RESET from CKE high to valid command >= tXPR                                         |

| tXSDLL                                | Self refresh exit to valid command with DLL must be >= tXSDLL                             |

| tXPDLL                                | Exit precharge power down with DLL to any valid command < tXPDLL                          |

| Additional DDR4 o                     | ompliance parameters                                                                      |

| tRASmin                               | ACTIVATE to PRECHARGE must be >= tRASmin                                                  |

| tRASmax                               | ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax                                   |

| tRCD                                  | ACTIVATE to READ/WRITE must be >= tRCD                                                    |

| tRP                                   | PRECHARGE to ACTIVATE/PRECHARGE must be >= tRP                                            |

| tRTP                                  | READ to PRECHARGE must be >= tRTP                                                         |

| tDRW                                  | READ to WRITE must be >= tDRW                                                             |

| tDWP                                  | WRITE to PRECHARGE must be >= tDWP                                                        |

| tDWR                                  | WRITE to READ must be > tDWR                                                              |

| tCCD_L                                | WRITE to WRITE, same bank group must be >= tCCD_L                                         |

| tRFC                                  | REFRESH to valid command (non_NOP/DESELECT) must be >= tRFC                               |

| tFAW                                  | Four ACTIVATE window (different banks) must be>= tFAW                                     |

| tRRD_L                                | ACTIVATE to ACTIVATE (same bank group) must be >= tRRD_L                                  |

| tRC                                   | ACTIVATE to ACTIVATE (same bank) must be >= tRC                                           |

| tREFI                                 | REFRESH to REFRESH <= tREFI*9                                                             |

## Post Process Compliance Tests (Continued)

| Compliance parameter   | Post-process compliance tests                                                  |  |  |  |  |  |

|------------------------|--------------------------------------------------------------------------------|--|--|--|--|--|

|                        | ance parameters (Continued)                                                    |  |  |  |  |  |

| tZQoper                | Long cal (normal operation) to valid command must be >= tZQoper                |  |  |  |  |  |

| tZQCS                  | Short calibration (normal operation) to any valid command must be > tZQCS      |  |  |  |  |  |

| tMRD                   | MRS (MODE Register Set) to MRS must be >= tMRD                                 |  |  |  |  |  |

| tMOD                   | MRS (MODE Register Set) to valid command must be >= tMOD                       |  |  |  |  |  |

| trefpden               | REFRESH to power down entry >= tREFPDEN                                        |  |  |  |  |  |

| tRDPDEN                | READ to power down entry >= tRDPDEN                                            |  |  |  |  |  |

| tWRPDEN                | WRITE to power down entry >= tWRPDEN                                           |  |  |  |  |  |

| tXPR                   | Exit RESET from CKE high to valid command >= tXPR                              |  |  |  |  |  |

| tXSDLL                 | Self refresh exit to valid command with DLL must be >= tXSDLL                  |  |  |  |  |  |

| tXPDLL                 | Exit precharge power down with DLL to any valid command < tXPDLL               |  |  |  |  |  |

| Additional LPDDR2/3 co |                                                                                |  |  |  |  |  |

| tRASmin                | ACTIVATE to PRECHARGE must be >= tRASmin                                       |  |  |  |  |  |

| tRASmax                | ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax                        |  |  |  |  |  |

| tRCD                   | ACTIVATE to READ/WRITE must be >= tRCD                                         |  |  |  |  |  |

| tRTP                   | READ to PRECHARGE must be >= tRTP                                              |  |  |  |  |  |

| tDRW                   | READ to WRITE must be >= tDRW                                                  |  |  |  |  |  |

| tDWP                   | WRITE to PRECHARGE must be >= tDWP                                             |  |  |  |  |  |

| tDWR                   | WRITE to READ must be > tDWR                                                   |  |  |  |  |  |

| tCCD                   | WRITE to WRITE, must be >= tCCD                                                |  |  |  |  |  |

| tRRD                   | ACTIVATE to ACTIVATE (different banks) must be >= tRRD                         |  |  |  |  |  |

| tFAW                   | Four ACTIVATE window (different banks) must be>= tFAW                          |  |  |  |  |  |

| tZQCL                  | Long calibration command to any valid command (or CKE low) must be > tZQCL     |  |  |  |  |  |

| tZQCS                  | Short calibration command to any valid command (or CKE low) must be > tZQCS    |  |  |  |  |  |

| tZQINIT                | Init calibration command to any valid command (or CKE low) must be > tZQINIT   |  |  |  |  |  |

| tZQRESET               | Reset calibration command to any valid command (or CKE low) must be > tZQRESET |  |  |  |  |  |

| tMRW                   | MRW command to any valid command (or CKE low) must be > tMRW                   |  |  |  |  |  |

| tMRR                   | MRR command to any valid command (or CKE low) must be > tMRR                   |  |  |  |  |  |

| tREFBW                 | Greater than 8 REFRESH all bank commands in tREFBW                             |  |  |  |  |  |

| tREFW                  | Required number of refresh commands occur in time perion <= tREFW              |  |  |  |  |  |

| tRFCab                 | REFRESH (all banks) to Active or Refresh must be > tRFCab                      |  |  |  |  |  |

| tRFCpb                 | REFRESH (per bank) to Activate (same bank) or REFRESH must be > tRFCpb         |  |  |  |  |  |

| tRPab                  | PRECHARGE (all banks) to ACTIVE (any bank) must be >= tRPab                    |  |  |  |  |  |

| tRPpb                  | PRECHARGE (per bank) to ACTIVE (same bank) must be >= tRPpb                    |  |  |  |  |  |

| tCKE                   | Duration of CKE high / low >= tCKE                                             |  |  |  |  |  |

| tXP                    | Exit Power down to any valid command >= tXP                                    |  |  |  |  |  |

| tCKESR                 | Duration of self-refresh >= tCKESR                                             |  |  |  |  |  |

| tDPD                   | Duration of power down to valid command >= tDPD                                |  |  |  |  |  |

| tXSR                   | Exit self-refresh to valid command >= tXSR                                     |  |  |  |  |  |

| tXSR                   | Exit self refresh to any valid command >=tXSR                                  |  |  |  |  |  |

## Post Process Compliance Tests (Continued)

|          | Post-process compliance tests                                                                       |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| LPDDR4   |                                                                                                     |  |  |  |  |

| tRASmax  | ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax                                             |  |  |  |  |

| tRASmin  | ACTIVATE to PRECHARGE must be >= tRASmin                                                            |  |  |  |  |

| tRCD     | ACTIVATE to READ/WRITE must be >= tRCD                                                              |  |  |  |  |

| tCCD     | READ -1 or any write (any bank) to READ-1 or any write (any bank) must be >= tCCD                   |  |  |  |  |

| tCCDMW   | Any write to MASKED WRITE (same bank) must be >= tCCDMW                                             |  |  |  |  |

| tRRD     | ACTIVATE-2 to ACTIVATE-2 (different banks) must be >= tRRD                                          |  |  |  |  |

| tMRW     | MRW-2 to any valid command must be >= tMRW                                                          |  |  |  |  |

| tMRR     | MRR-1 to any valid command must be >= tMRR                                                          |  |  |  |  |

| tRPab    | PRECHARGE (all banks) to ACTIVATE-2/REFRESH (any bank) >= tRPab                                     |  |  |  |  |

| tRPpb    | PRECHARGE (per bank) to ACTIVATE-2 (same bank) or REFRESH (same bank or all banks) must be >= tRPpb |  |  |  |  |

| tXSR     | Exit self refresh to any valid command >= tXSR                                                      |  |  |  |  |

| tPPD     | Precharge (any bank to Precharge (any bank) must be >= tPPD                                         |  |  |  |  |

| tRFCab   | REFRESH (all banks to ACTIVATE-2 or REFRESH >= tRFCab                                               |  |  |  |  |

| tRFCpd   | REFRESH (per bank) to ACTIVATE-2 (same bank) or REFRESH > tRFCpb                                    |  |  |  |  |

| tCKE     | Duration of CKE high/low >= tCKE                                                                    |  |  |  |  |

| tESCKE   | Self Refresh Entry command to CKE low must be >= tESCKE                                             |  |  |  |  |

| tCMDCKE  | Any valid command to CKE low must be >= tCMDCKE                                                     |  |  |  |  |

| tCKEHCMD | Exit powerdown to any valid command >= tCKEHCMD                                                     |  |  |  |  |

| tSR      | Self refresh entry to self refresh exit >= tSR                                                      |  |  |  |  |

| tMMRRIa  | Exit powerdown to MRR >= tMRRIa (where tMRRIa = tXP (tCKEHCMD) + tMRRI)                             |  |  |  |  |

| BL16     | Write/Read/Precharge - BL16 - Select these tests if your system uses fixed BL16                     |  |  |  |  |

| BL32     | Write/Read/Precharge - BL16 - Select these tests if your system uses fixed BL32                     |  |  |  |  |

| BL OTF   | Write/Read/Precharge - BL16 - Select these tests if your system uses Burst length OTF (on the fly)  |  |  |  |  |

| MWtoP    | MASKED WRITE-1 to PRECHARGE (same bank) >= MWtoP                                                    |  |  |  |  |

| MWtoR    | MASKED WRITE-1 to READ (same bank) >= MWtoR                                                         |  |  |  |  |

| RFtoLAT  | RD_FIFO to ZQCALLATCH >= RFtoLAT                                                                    |  |  |  |  |

| RFtoLAT  | RD_CALIBRATION to ZQCALLATCH >= RFtoLAT                                                             |  |  |  |  |

| RFtoLAT  | MRR to ZQCALLATCH >= RFtoLAT                                                                        |  |  |  |  |

| WFtoLAT  | WR_FIFO to ZQCALLATCH >= WFtoLAT                                                                    |  |  |  |  |

| WFtoLAT  | MASKED WRITE-1 to ZQCALLATCH >= WFtoLAT                                                             |  |  |  |  |

| tZQCAL   | ZQCALSTART to ZQCALLTACH >= tZQCAL                                                                  |  |  |  |  |

| tZQLAT   | ZQCALLATCH to any valid command >= tZQLAT                                                           |  |  |  |  |

| tZQRESET | ZQCALRESET to any valid COMMAnd >= tZQRESET                                                         |  |  |  |  |

## Post Process Compliance Tests (Continued)

| Compliance parameter | ·                                                                                                    |  |  |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| LPDDR4               | Refresh tests                                                                                        |  |  |  |  |  |

| tREFI*9              | REFRESH command to REFRESH command must be <=tREFI*9                                                 |  |  |  |  |  |

| tREFW                | Required number of refresh commands occur in time period <= tREFW                                    |  |  |  |  |  |

| tRFCab               | Refresh (all banks) to Activate or Refresh must be > tRFCab                                          |  |  |  |  |  |

| tRFCpb               | Refresh (per bank) to Activate (same bank) or Refresh must be > tRFCpb                               |  |  |  |  |  |

| tREFI*2              | No more than 16 refresh commands occur in time period (tREFI *2)                                     |  |  |  |  |  |

| LPDDR4               | Power down and self-refresh tests                                                                    |  |  |  |  |  |

| tXSR                 | Exit Self-Refresh to valid command >= tXSR                                                           |  |  |  |  |  |

| tXP                  | Exit power down to valid command >= tXP                                                              |  |  |  |  |  |

| tESCKE               | Self-Refresh entry command to CKE low >= tESCKE                                                      |  |  |  |  |  |

| tCMDCKE              | Any valid command to CKE low >= tCMDCKE                                                              |  |  |  |  |  |

| tCKEHCMD             | Exit powerdown to any valid command >= tCKEHCMD                                                      |  |  |  |  |  |

| tSR                  | Self refresh entry to self refresh exit >= tSR                                                       |  |  |  |  |  |

| tMRRIa               | Exit powerdown to MRR >= tMRRIa (tXP + tMRRI)                                                        |  |  |  |  |  |

| tCKE                 | Duration of CKE high/ low >= tCKE                                                                    |  |  |  |  |  |

| IUNE                 | Duration of the high tow >= toke                                                                     |  |  |  |  |  |

| LPDDR4               | Write/Read/Precharge/Cal - BL16 - Select these tests if your system uses fixed BL 16                 |  |  |  |  |  |

| RtoWBL16             | READ16 to any write >= RtoWBL16                                                                      |  |  |  |  |  |

| WtoRBL16             | WRITE16 to READ16 >= WtoRBL16                                                                        |  |  |  |  |  |

| RtoRBL16             | READ16 to PRECHARGE (same bank) >= RtoRBL16                                                          |  |  |  |  |  |

| WtoPBL16             | WRITE16 to PRECHARGE (same bank) >= WtoPBL16                                                         |  |  |  |  |  |

| RtoLATBL16           | READ32 to ZQCALLATCH >= RtoLATBL16                                                                   |  |  |  |  |  |

| WtoLATBL16           | WRITE32 to ZQCALLATCH >= WtoLATBL16                                                                  |  |  |  |  |  |

| LPDDR4               | Write/Read/Precharge/Cal - BL32 - Select these tests if your system uses fixed BL 32                 |  |  |  |  |  |

| RtoWBL32             | READ32 to any write >= RtoWBL32                                                                      |  |  |  |  |  |

| WtoRBL32             | WRITE32 to READ16 >= WtoRBL32                                                                        |  |  |  |  |  |

| RtoRBL32             | READ32 to PRECHARGE (same bank) >= RtoRBL32                                                          |  |  |  |  |  |

| WtoPBL32             | WRITE32 to PRECHARGE (same bank) >= WtoPBL32                                                         |  |  |  |  |  |

| RtoLATBL32           | READ32 to ZQCALLATCH >= RtoLATBL32                                                                   |  |  |  |  |  |

| WtoLATBL32           | WRITE32 to ZQCALLATCH >= WtoLATBL32                                                                  |  |  |  |  |  |

|                      |                                                                                                      |  |  |  |  |  |

| LPDDR4               | Write/Read/Precharge/Cal - BL OTF - Select these tests if your system uses fixed BL OTF (on the fly) |  |  |  |  |  |

| RtoWBL160TF          | READ32 to any write >= RtoWBL160TF                                                                   |  |  |  |  |  |

| WtoRBL160TF          | WRITE32 to READ16 >= WtoRBL160TF                                                                     |  |  |  |  |  |

| RtoRBL160TF          | READ32 to PRECHARGE (same bank) >= RtoRBL160TF                                                       |  |  |  |  |  |

| WtoPBL160TF          | WRITE32 to PRECHARGE (same bank) >= WtoPBL160TF                                                      |  |  |  |  |  |

| RtoWBL32otf          | READ32 to any write >= RtoWBL320TF                                                                   |  |  |  |  |  |

| WtoRBL320TF          | WRITE32 to READ16 >= WtoRBL320TF                                                                     |  |  |  |  |  |

| RtoRBL320TF          | READ32 to PRECHARGE (same bank) >= RtoRBL320TF                                                       |  |  |  |  |  |

| WtoPBL320TF          | WRITE32 to PRECHARGE (same bank) >= WtoPBL320TF                                                      |  |  |  |  |  |

| RtoLATBL160TF        | READ32 to ZQCALLATCH >= RtoLATBL320TF                                                                |  |  |  |  |  |

| WtoLATBL160TF        | WRITE32 to ZQCALLATCH >= WtoLATBL320TF                                                               |  |  |  |  |  |

| RtoLATBL320TF        | READ32 to ZQCALLATCH >= RtoLATBL320TF                                                                |  |  |  |  |  |

| WtoLATBL320TF        | WRITE32 to ZQCALLATCH >= WtoLATBL320TF                                                               |  |  |  |  |  |

|                      | ·                                                                                                    |  |  |  |  |  |

### LPDDR Decoder (B4661A-2FP/2TP/2NP)

#### Key features

- Decodes LPDDR, LPDDR2, LPDDR3 and LPDDR4 commands and MRS commands.

- Enables fast physical address trigger setup for LPDDR2/3.

Using the LPDDR decoder, valid read and write commands are decoded to include row and column addresses and the complete data burst associated with the command.

Figure 17. LPDDR4 decode in listing window.

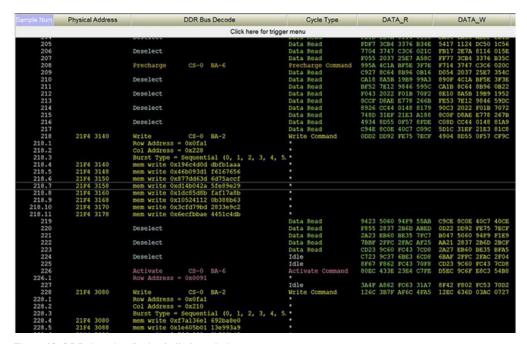

## Physical address conversion tool in both DDR3/4 and LPDDR2/3 decoders with integrated trigger creation

Setting up a trigger on a specific physical address to obtain the corresponding data bus can be very tedious. The physical address trigger tool is included in the B4661A DDR decoder and LPDDR decoder options. The trigger tool allows you to automatically create a trigger on a specific physical address without having to go through a step-by-step trigger add-in. The physical address trigger tool incorporates a user-friendly interface to help the user quickly setup the trigger. DDR2/3/4 and LPDDR2/3 are covered by the physical address trigger tool. LPDDR4 is not covered by the physical address trigger tool.